Gowin FPGA の OPEN_DRAIN の挙動

Tang Nano 9K に搭載されている Gowin の FPGA(GW1NR-9)について、I/O に設定可能な OPEN_DRAIN というオプションの挙動を確認しました。結論としては、OPEN_DRAIN の ON/OFF によらずプルアップ抵抗の有無が選択できること、0 を出力すると 0V が出力されることが分かりました。

OPEN_DRAIN オプション

Gowin の FPGA は(他のメーカーでも同様だと思いますが)I/O をオープンドレインに設定できます。物理制約ファイルに次のように記述します。

IO_PORT "sig" IO_TYPE=LVCMOS33 PULL_MODE=NONE OPEN_DRAIN=ON;

OPEN_DRAIN は ON か OFF を指定できます。デフォルトでは OFF でプッシュプル出力です。

OPEN_DRAIN=ON に設定した I/O に対し 0 を書くと NMOS が導通し 0V が出力されます。1 を書くと NMOS が遮断しハイインピーダンスとなります。

PULL_MODE との組み合わせ

PULL_MODE は I/O のプルアップ/プルダウンを制御します。UP、DOWN、KEEPER、NONE のいずれかを指定できます。デフォルトでは UP のようです。一般的にプルアップ/プルダウンは入力ポートで使う機能ですが、GW1NR-9 では出力に設定した端子でも PULL_MODE は有効に機能するようです。

OPEN_DRAIN=ON かつ PULL_MODE=UP と設定する(あるいは PULL_MODE を設定せずデフォルトとする)と、0 を書くと 0V が、1 を書くと電源電圧(バンクにより異なる)が出力されます。

OPEN_DRAIN=ON かつ PULL_MODE=NONE と設定すると、0 を書くと 0V が、1 を書くとハイインピーダンスが出力されます。オープンドレイン出力と言うとき、一般的に想像するのはこちらの設定かなと思います。

1=0V じゃなくて 0=0V だ!

オープンドレイン出力は NMOS のゲートを制御するわけですから、電子回路的に考えれば 1 を書くと 0V が、0 を書くとハイインピーダンスが出力されるように思えます。しかし、実験の結果、そうではありませんでした。

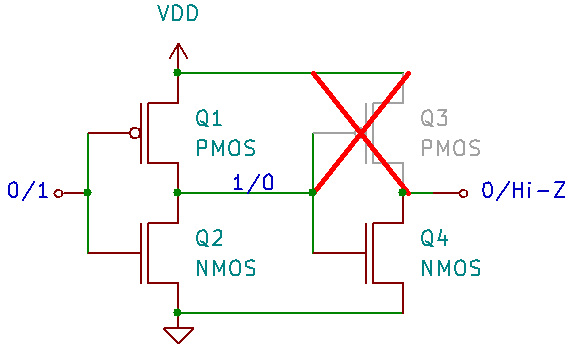

FPGA の I/O の出力部分はおそらく上図のようになっていて、オープンドレイン出力のときは Q3 が無効化される仕組みなのだと思います。(Kenta IDA さんがヒントをくださいました)

プッシュプル出力のときは 0 を書いたら 0V が、1 を書いたら VDD が出力されて欲しいですから、そのために Q1 と Q2 を使って論理を反転しなければなりません。その回路の影響で、オープンドレイン出力に設定しても 0 で 0V が出力される、と考えると納得できますね。

この記事を参照しているブログ内記事はありません。